在现代计算机系统中,CPU如何高效地读写内存数据是一个关键话题。虽然表面看似简单,实际上该过程涉及多个软硬件组件的协同工作。本文将通过结构化分析,揭示CPU读写内存过程中复杂而精妙的运作机制。

1. 谁来告诉CPU读写内存

CPU的操作主要通过程序指令来执行,这些指令通常由编译器生成。编译器将高级语言翻译为机器指令,指示CPU如何操作内存。根据不同的架构,如精简指令集(RISC)和复杂指令集(CISC),CPU可能采用不同的方法来执行读写操作。

2. 两种内存读写

从功能上讲,CPU读写内存有两种基本操作:

- 数据读写:通过特定的加载/存储指令(如Load/Store)来操作内存。

- 指令读取:从内存中获取下一条要执行的指令。

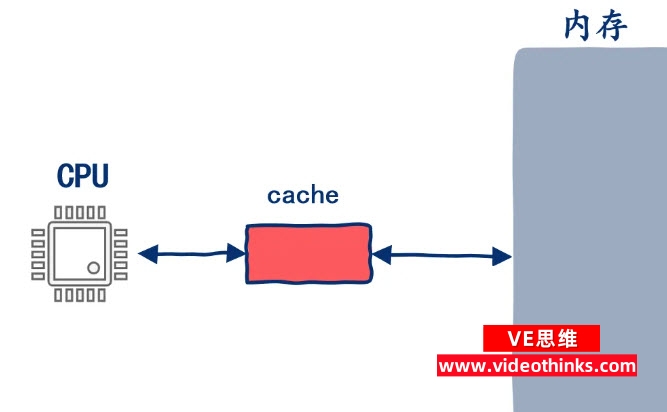

3. 缓存的作用与实现

为了弥补内存速度与CPU速度的巨大差异,计算机系统引入了缓存(Cache)。缓存利用程序的局部性原理,将常用数据放置于速度更快但容量较小的SRAM中。这样在大多数情况下,CPU可以从缓存中快速获取数据,显著提升整体性能。

4. 缓存同步与更新策略

当CPU需要写内存时,更新缓存与内存的一致性成为一个问题。目前主要有两种策略:

- 同步更新(Write-through):每次写入缓存都同步更新内存。

- 异步更新(Write-back):写操作只更新缓存,等缓存块被替换时再更新内存。这种方法能显著提升性能,但更加复杂。

5. 多级缓存与其操作原理

现代CPU通常采用多级缓存架构(L1、L2、L3 Cache)。CPU访问内存首先在L1 Cache查找,不命中则到L2、L3 Cache,最后才访问主内存。每一级缓存速度递减但容量增加,最大限度地提升系统性能。

6. 多核处理器中的缓存一致性问题

多核处理器引入了缓存一致性问题。当多个核心共享内存,且每个核心有自己的缓存时,必须维护缓存的一致性。协议如MESI(Modified, Exclusive, Shared, Invalid)被广泛应用于解决此问题,确保各核心缓存中的数据和内存中的数据保持一致。

7. 虚拟内存机制

虚拟内存通过给进程一个“虚拟”地址空间来简化编程。CPU在执行指令时会通过内存管理单元(MMU)将虚拟地址转换为物理地址。如果缓存不命中,还可能需要访问更慢的磁盘数据。

8. 总结

CPU读写内存过程涉及多种硬件组件和复杂的软硬件协同,这一过程包括多级缓存、缓存一致性协议以及虚拟内存机制。理解这一过程不仅有助于更好地编写高效程序,也能更深入地理解现代计算机系统的复杂性。

通过优化利用缓存,程序员不仅可以提升程序性能,还可以更好地理解和利用现代计算机架构的各种高级特性。希望这篇文章能对您深入理解CPU与内存的交互机制有所帮助。